返场7天,加推15套开发版!

售完即止!

返场活动

上次活动结束后,很多学员询问我还有没有FPGA(课程+板子)套件购买,因此跟老师申请多了15套回馈给大家,错过上次活动的学员抓住机会哦~

返场时间:6月17日-23日 最后7天

发货说明:

6月15日以前购买的用户,将在本轮众筹课程结束后15天内发货;

返场期间(6月17-23日)购买的用户,将在返场结束后15天内发货;

领 取 更 多 优 惠 ?

对此众筹有任何疑问,请添加客服微信:shanny3344

备注:咨询FPGA,或者扫一扫以下二维码哦

返场7天,加推15套开发版

售完即止!

行业大咖他们这样说

FPGA目前行业现状是怎样的?

1、FPGA是软硬件开发是门槛最高的行业之一,FPGA采用HDL(硬件描述语言)直接从最底层开发算法,对工程师的要求极高,没有很好的方法,入门很难;

2、5G的发展,深度学习,自动无人驾驶的兴起,传统纯软件处理方式已经不能满足实时性要求,而FPGA的并行加速能力,是必然选择;

3、FPGA属于半导体行业无法缺少的一块,而国内半导体正处在蓬勃的发展阶段,各类高科技公司需求旺盛;

4、相比与其他工程师岗位,FPGA工程师待遇普遍不错,无线通信方向的工程师更是供不应求,大型通信公司从事无线通信开发的应届研究生年薪普遍达到30万,经验丰富的FPGA工程师更是千金难求。

我们为什么做这次众筹?

1、5G的兴起,无线通信方向必然是未来FPGA的开发热点;

2、国内FPGA无线通信领域的教材太少,且大部分教程仅流与形式,质量不高;

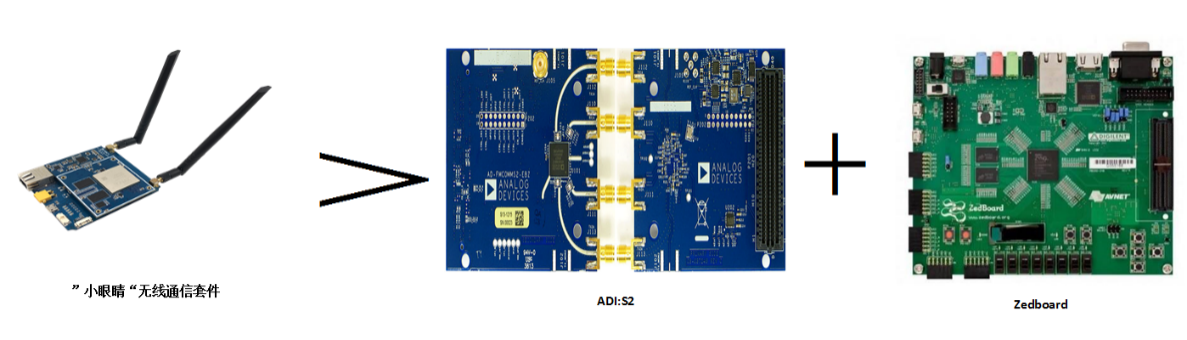

3、从事无线通信的开发软硬件成本极高,且国外开发的SDR售后差,售后周期长,我们入门就走过很多的弯路;

4、基于FPGA的无线通信开发门槛高,几乎涉及了FPGA开始的所有高级技巧:面积和速度的置换,矩阵的处理,数学运算等,学习基于无线通信的FPGA操作技巧,能使FPGA开发水平上升到一个更高的层次;

5、在这几年深度学习,自动无人驾驶等行业的FPGA招聘中,有无线通信开发经验的工程师往往会有更多的竞争优势;

希望这次众筹的课程能帮到大家什么?

本课程由浅入深,摒弃传统教程离散的模块呈述方式:讲解语法,工具的使用、IP的调用等。本教程以无线通信系统搭建为主线,从项目立项,需求确认,算法建模,编码,量产等多个环节讲解内容,涉及FPGA工具的安装,Verilog语言的学习,模块的划分,算法的定点等多个环节,实战讲解FPGA处理的:FFT,组帧,乒乓操作,矩阵变换,数学运算等多类处理技巧。总括全局,一览众山小。

众筹课程介绍

1、我们不想告诉大家怎么点亮流水灯,也不想讲些无关痛痒的业内共识,但我们相信通过本次课程的学习,大家对FPGA和无线通信的开发会站在一个更高的层次。

2、不仅仅翻译原始文档(国内的很多这种教程),尊重原厂文档并站在产品的角度开发FPGA。

3、一块配套教程并远低于其它FPGA SDR的开发板,并在后续持续推出兼容各类应用的底板。

4、FPGA原理图设计及审核。

5、DDR3的PCB布局及操作技巧;

6、ZYNQ平台的搭建;

7、PS和PL的调试技巧;

8、MATLAB的无线通信算法仿真概述;

9、算法的定点;

10、各类矩阵的处理方法:相乘,相加;

11、FFT IP的仿真模型及使用;

12、AD9361的硬件设计及布局注意事项;

13、射频调试技巧及应用实例;

14、FCC,CE认证的一些常识;

本期众筹课程有哪些亮点?

1、通过本课程的学习,您将从最底层了解FPGA的构造,从系统层面从事FPGA相关工作的开发;

2、熟悉FPGA的各种处理技巧;

3、深入高速通信及无线通信的开发流程及技巧;

4、和国内多家FPGA原厂工程师深入交流;

5、MYMINIEYE将和大家一起畅聊这些年在北京,深圳等FPGA开发趣事和行业动态;

用户购买视频学习后,将会获得哪些收益?

1、不仅仅得到的是理论解答,从项目立项,芯片选型,开发验证等各个角度讲解产品的应用开发;

2、大量可直接使用的工程实践源码开放,matlab算法和和Modesim仿真一致;

3、中科院,紫光等一线工程师和您一起解决算法和代码问题,涉及无人机,VR等多行业应用的分享;

适用人群有哪些?

1、有志于从事FPGA开发和无线通信开发的在校大学生及教师等;

2、各类从事FPGA软件开发(如高级辅助驾驶,深度学习),想深入理解FPGA原理的工程师;

3、对数字信号处理感兴趣的FPGA开发工程师;

4、从事无线通信系统开发的公司,用于原型验证;

5、FPGA技术到了瓶颈,想要提升技能,找到更快突破口的工程师;

6、想了解和接触半导体行业的各位软硬件工程师们;

每个套装的详细课程大纲

| 基础教程 | |

无线系统简介及应用(直播内容) 1、SDR的前景 2、实现平台介绍 3、本平台框图架构介绍 4、FPGA与数字信号处理 | 内容简介: 1、在FPGA招聘中,为什么有无线通信开发经验的工程师会更受欢迎? 2、发起本套FPGA开发板众筹的初衷? 3、课程讲哪些内容,和传统教程的区别? 4、本次众筹开源哪些内容 5、资源及团队介绍? |

1.1 FPGA SOC系统简介(ZYNQ:7030) 1、应用场景介绍(图传,应急指挥,影像) 2、SOC系统软硬件资源; 3、系统平台系统架设计 4、FPGA的资源; 5、时钟系统; 6、机械尺寸; | 内容简介: 1、FPGA开发前期该怎样选择合适的器件? 2、SOC系统的优势? 3、Xilnx, altera, lattice,国产FPGA的特点及定位? 4、为什么选择ZYNQ做无线通信开发? |

1.2系统硬件设计(FPGA硬件,射频放进阶,提及此内容) 1、FPGA的电源设计及上电时序; 2、FPGA的硬件原理设计; 3、FPGA PCB审核及硬件调试; | 内容简介: 1、FPGA硬件设计有哪些坑? 2、FPGA原理图设计应该参考哪几个资料文档? 3、怎样确认FPGA的原理图设计没有问题? |

1.3 Veirlog 中的两个always 1、Verilog中的时序电路和组合电路; 2、Vivado 使用安装,操作流程; 3、Vivado中的调试,debug; 4、30分钟讲解清串口通信 | 内容简介 1、Verilog写打印Hello world有多难? 2、Verilog学习最值得推荐的资料? 3、写代码是后应该注意的问题点? 4、代码规范? 5、选择哪个版本的工具进行工程的开发最合适? 6、工具的一些使用技巧? 7、软件License的获取? |

1.4 SOC系统的逻辑开发(ZYNQ PL介绍) 1、按键 led(IO); 2、时钟倍频,分频; 3、锁相环详解; 4、IP core调用,使用详解(datasheet解读) | 内容简介: 1、在FPGA都有哪些可使用的资源,ZYNQ有什么不同之处? 2、FPGA设计中时钟资源的利用及时钟的规划? 3、IP Core和源语的使用? 4、哪些功能适合在PL端开发? |

1.5 SOC系统的软件开发(ZYNQ PS介绍) 1、Zynq系统框架介绍; 2、PS时钟树; 3、PS IO资源分配; 4、EMIO & MIO; 5、建PS系统; | 内容简介: 1、ZYNQ中都有哪些软件资源? 2、PS开发应该参考哪些资料? 3、ZYNQ的IO特点? 4、PS IO不够怎么办? |

1.6 片内总线协议(2~3节课) 1、AXI发展 2、AXI4 3、AXI stream 4、AXI4 lite | 内容简介: 1、什么是AXI总线? 2、AXI总线的作用,相比于FPGA+ARM(外挂)的优劣势? 3、AXI Stream和AXI4 lite的协议差别及具体工程中的选择? |

1.7 复杂SOC系统的搭建及开发(一) 1、PL与PS组建系统; | |

1.8 复杂SOC系统的搭建及开发(二) 1、PS串口发送命令到PL; 2、AXI lite数据交互; | 内容简介: 1、怎样搭建一个复杂SOC系统? 2、怎样实现PL和PS的数据交互? 3、AXI总线的操作? |

1.9 Modelsim与vivado联合调试环境() 1、编译库 2、Vivado系统设置 3、实际跑一个仿真流程 | 内容简介: 1、怎样进行VIVADO和Modesim的联合调试及仿真? 2、怎样编译库? 3、实际仿真都会产生哪些文件,都有什么作用? |

| 进阶教程 | |

2.1 zynq系统PS与PL互联 1、PL和PS交互方式; 2、调试技巧 3、总线大数据交互; 4、详解HP,GP(master/slave)模式,建交互系统工程; | 内容简介: 1、PL和PS的通信方式; 2、哪些适合在PL中实现,哪些更适合在PS中实现? 3、选择哪种接口方式更合适? |

2.2 zynq上运行linux系统(一) 1、系统运行环境搭建 2、Fsbl生成 3、Bootbin生成 | |

2.3 zynq上运行linux系统(二) 1、设备树生成 2、Uboot生成 3、内核修改 | |

2.4 zynq上运行linux系统(三) 1、驱动 2、应用 | 内容简介: 1、从哪里得到开发linux需要的资料? 2、怎样选择合适的linux版本进行开发? 3、怎样完成完整的系统搭建? 4、Uboot的编译,FSBL编译,Kernel编译? 5、设备树的修改? 6、系统搭建中需要注意的问题? |

2.5 PS外设的操作; 1、1000M以太网的使用; 2、提供源码; 3、演示以太网通信; | 内容简介: 1、怎样在zynq进行1000以太网开发? 2、1000M开发应注意哪些内容? |

2.6 DDR3的硬件设计 1、DDR3原理 2、DDR3硬件设计注意事项 | 内容简介: 1、DDR3设计该怎么选型? 2、怎样设计你的DDR3原理图? 3、DDR3布局布线中有哪些坑? 4、怎样验证你的DDR3布线是没有问题的? |

2.7 zynq系统的DDR3的操作(一) 1、DDR3控制器 | |

2.8 zynq系统的DDR3的操作(二) 1、DDR3控制器 2、数据共享 | 内容简介: 1、地址映射方式? 2、DDR3的使用? 3、DDR3设计中要知道的几个公开的秘密 4、DDR3设计中数据的交互效率? |

2.9 zynq系统的数据共享 1、DDR3仿真 2、DDR3 PL和PS的互操作; | 内容简介: 1、什么时候用PS端的DDR3会比较合适? 2、DDR3该怎样Debug? 3、怎么样去系统仿真DDR3? |

2.10 驱动代码(AD9361配置,开放源码) 1、AD936X配置流程 2、配置AD936X相关寄存器 3、相关小工具的使用 4、AD936X配置的源码 | 内容简介: 1、哪些寄存器需要特别关注? 2、怎样调节IOdelay? |

2.11 AD936X的硬件调试,AD936X的硬件设计 1、AD936X原理图设计; 2、射频器件的选型; 3、PCB布局布线; | 内容简介: 1、射频的原理图及PCB布局需要注意? 2、晶振选择要注意什么? |

2.12 射频调试 1、射频调试 | 内容简介: 1、发送调试的应关注的指标? 2、接收调试手段及关注的指标? 3、怎样测试系统灵敏度? |

2.13 FCC,CE认证 1、FCC,CE介绍; | 内容简介: 1、产品出口欧美应注意的问题; 2、产品一致性问题; 3、品控及风险; |

| 高级教程 | |

3.1 无线通信算法介绍 1、无线通信系统的发展; 2、无线通信系统总括; 3、系统的关键技术点; | 内容简介: 1、系统架构? 2、通信系统设计应该注意哪些问题? 3、COFDM应用场景? |

3.2 扰码 1、扰码原理及matlab仿真; 2、扰码verilog; 3、数据仿真及比对; | 内容简介: 1、扰码在通信系统的应用; 2、扰码的matlab仿真; 3、扰码Verilog代码的编写及Modesim代码的编写; |

3.3 交织 1、交织原理及matlab仿真; 2、交织verilog; 3、数据仿真及比对; | 内容简介: 1、交织的种类及在通信系统中的作用; 2、矩阵变换的常用做法; 3、交织的Verilog的代码及Matlab仿真; |

3.4 调制及映射方式(QPSK,16QAM) 1、调制原理及matlab仿真; 2、调制verilog; 3、数据仿真及数据比对 | 内容简介: 1、通信系统的调制种类及应用场景; 2、QPSK,16QAM matlab代码仿真; 3、16QAM及QPSK Verilog代码及Modesim仿真 |

| 3.5 FFT:(2~3节课) 1、FFT 的Matlab算法原型验证; 2、FFT IP Core的使用技巧; 3、FFT的Verilog代码及仿真 | 内容简介: 1、FFT的调试技巧? 2、FFT设计中的一些坑? 3、FFT保护间隔用多长? |

3.6 数据组帧 1、数据组帧介绍 | 内容简介: 1、基带算法组帧的重要性? 2、组帧设计应注意的问题? 3、提供组帧的Verilog源码及Modesim仿真? |

3.7 滤波器(matlab仿真插值,抽取) 1、滤波器的设计; 2、Matlab源码及Verilog 源码 | 内容简介: 1、基带通信算法中改怎样设计滤波器 2、滤波器的作用 |

3.8 定点技巧(1~2节课) 1、定点技巧; | 内容简介: 1、怎么实现浮点到定点 2、浮点到定点的评判标准是什么? 3、浮点到定点的Matlab模型 4、浮点到定点的Verilog代码及Modesim仿真 |

3.9FPGA与数学运算:DSP资源介绍 1、DSP硬件资源介绍 | 内容简介: 1、为什么在设计中不适用现成IP CORE实现相应数学运算? 2、ZYNQ中DSP48e的硬件结构及特点; |

3.10 FPGA与数学运算: 1、DSP48e实现累加,乘加,加减的技巧 | 内容简介: 1、累加设计,乘减,加减verilog源码及Modesim仿真 |

3.11 FPGA与数学运算 1、数学运算中乘法,除法,求模的转换及技巧 | 内容简介: 1、什么时候要用乘法,什么时候需要将乘法做转换; |

3.12 系统同步----滑动累加 1、滑动累加的原理及代码 | 内容简介: 1、通信系统中数据同步的特点 |

3.13 LDPC编码(待定) 1、LDPC编码技术 | 内容简介: 1、Turbo,卷积等编码的特点; 2、LDPC编码的Verilog源码及Modesim仿真 |

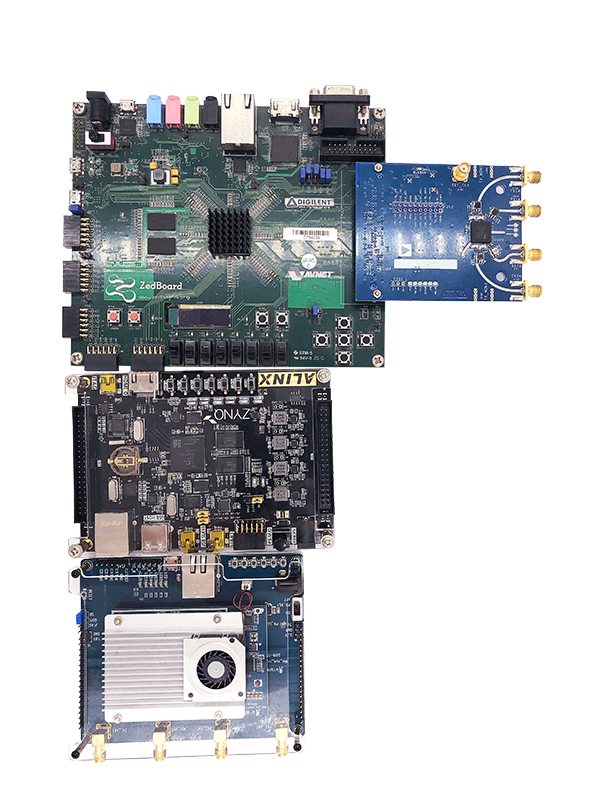

开发板的详细介绍

小眼睛FPGA无线通信开发板

XILINX(ZYNQ)+ADI(AD936X)高性能无线通信开发套件(众筹主板底板拥有4天线输出)

核心板:(众筹版本增加模式选择开关及标准电源接口)

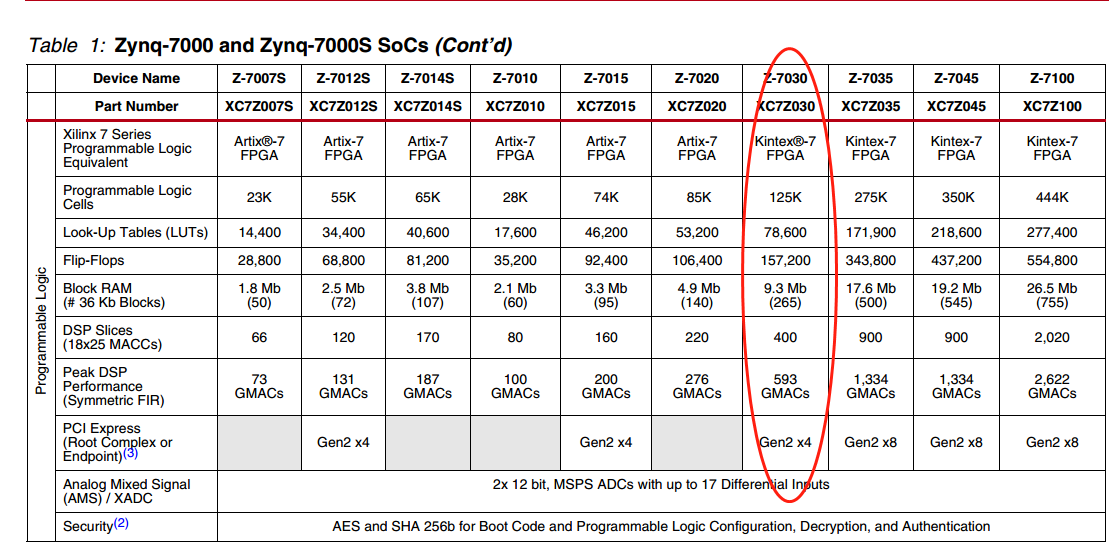

FPGA:主芯片ZYNQ(XC7Z030-2FFG676I):

a) 内置双核Cortex-A9;

b) 125K Logic Cell逻辑资源,157K FF;

c) 9.3M存储资源;

d) 工业级,-2速度等级

e) PIN to PIN兼容更大规模XC7Z035,XC7Z045;

DDR3:两块2Gbit 高性能DDR3,速度达1066MBbps;

Flash: 256Mbit 4线QSPI Flash;

DC-DC:ADP5054ACPZ_1(ADI)

晶振:SIT1602BI-40.00M\ SIT1602BI-33.333.00M(SimTime)可编程高精度晶振

连接器:60pin高性能连接器(3个);

射频板(众筹版本版型略大,采用4天线,支持更多频段,布局更合理):

射频主芯片:AD9363ABCZ(ADI 零中频输入射频);

巴伦:2450BL15B050_v3

LNA低噪放:SKY65971-11

1000M以太网:88E1518-NNB2_0;

Micro-USB接口:USB3320

双串口:TXS0102DQER

JTAG:下载接口

SD卡:TXS02612RTWR;

按键:(众筹版本增加4个按键)

LED流水灯:

ZYN7030+AD9363(FPGA核心芯片资源是Zedboard:ZC7020的两倍),价格不到市面开发版的一半,量产的系统更适合通信原型验证。

亮点:

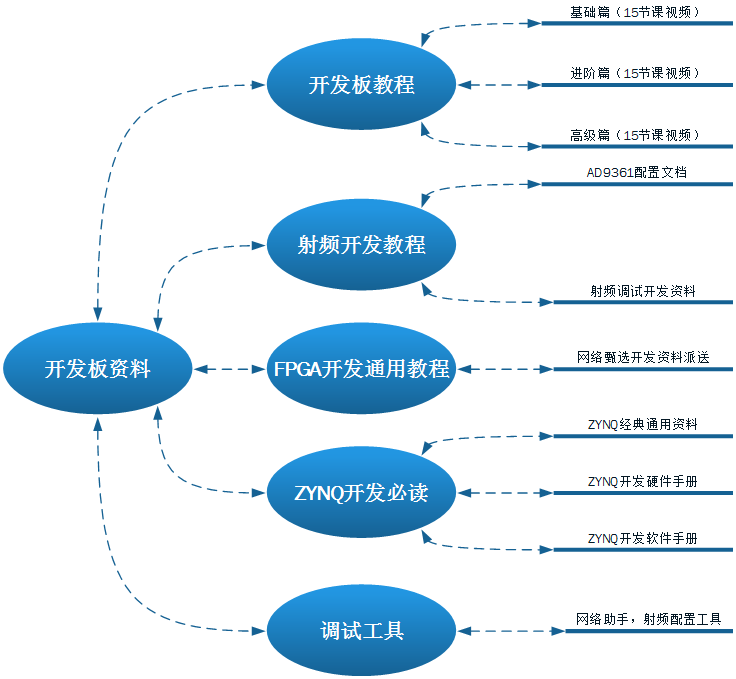

1、 丰富的实战资料(记住:不是告诉你点流水灯的那种!)配套40节原创实战课程涵盖FPGA处理的各类高级处理技巧(不断更新中···);

2、 提供用户手册、原理图、芯片手册、出厂代码、实战的Verilog源码;

3、涵盖各类算法处理技巧(矩阵变换、指数运算,迭代,乒乓操作,组帧等)、linux最小系统、XDC文件(UCF文件)、Matlab源码、testbentch、Modesim仿真工程;

4、 ISO9001认证自有工厂,品质更可靠;

5、 多位原厂工程师及一线技术专家重磅推荐。

资料导图:

学生或新手能不能学会?

本教程从产品和应用的角度对FPGA进行讲解,以浅显易懂的方式描述,并充分结合并尊重原厂文档,方便还在大学的各位初学者更早的接触市场需求和工程应用,帮助大家走更少的弯路,真正做到以点带面,触类旁通。

老手有没有必要入手?

我们接触过很多团队,有些团队有很好的算法,但往往由于缺少对工程的经验和FPGA的深入了解,定点不精准,很好的算法,但却需要很大的逻辑规模;也有一些团队:实战经验多,但往往算法模型和FPGA代码没法对应,最终导致功能实现没有问题,但真正遇到问题却很难定位。这些年,不敢说团队什么都会,但确实踩过很多坑,所以希望能通过我们的经验对大家有更多的启发,更快的完成自身产品的迭代。

众筹成功后,有哪些服务?

1、远低于市场售价的FPGA SDR开发板;

2、和众多原厂工程师进行技术交流;

3、持续的技术支持及FPGA开发答疑;

4、一系列涵盖FPGA硬件设计,无线通信系统开发,射频调试等课程;

5、 提供交流群:纯技术,十分活跃,众筹用户可与老师面对面交流;

6、永久的售后服务:拒绝一次性买卖,购买一次,享受终生售后服务。

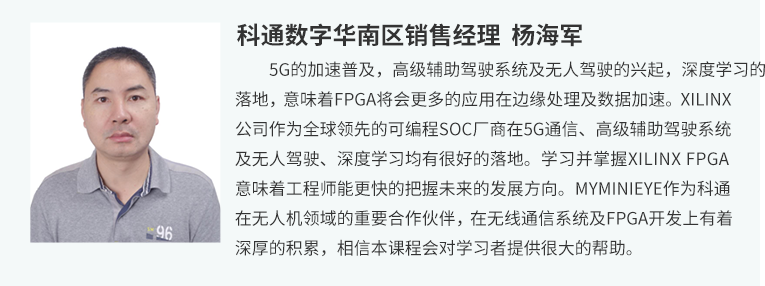

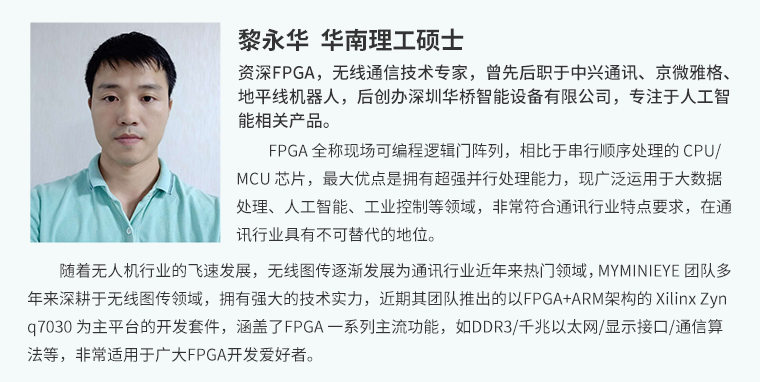

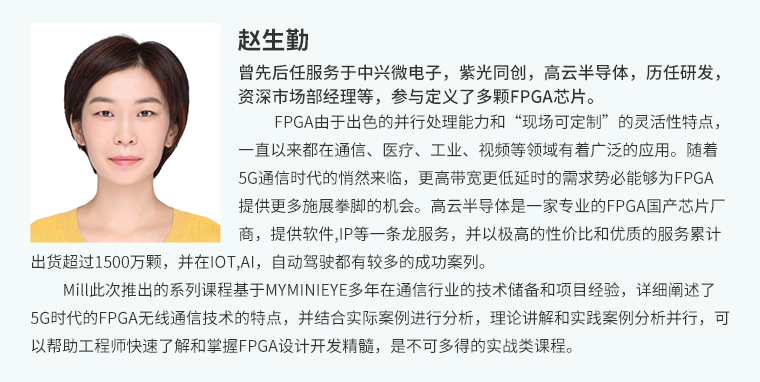

讲师团队介绍

MYMINIEYE(深圳市我是你的眼科技有限公司)成立于2015年。团队创始人在无线通信领域有近20年的从业经验,开发的各类无线通信产品涵盖:无人机,无人船,航模,房车,扫地机器人等多个不同领域。在全球,MYMINIEYE团队的无线通信技术服务了全球超过100多个国家的2000多个客户。MYMINIEYE核心研发团队来自于中科院,华为技术,紫光集团等国内知名学府及通信企业,拥有领先的基带算法和FPGA开发能力,也是国内少数拥有最底层LDPC编解码开发并量产的公司。

.参与众筹后,如何发货?如何开发票

提交订单时请确保收获信息准确无误,众筹结束后15天内,统一安排发货哦

有疑问请添加客服姐姐

QQ:1126680104

微信:shanny3344,或者扫一扫二维码,备注:咨询FPGA

开发票请添加客服姐姐:QQ:3430715554,备注:FPGA开票

---------------------------------------------------------------------------------------

常见问题

1、 开发板是现成的吗?是什么型号的?

答:众筹课程使用的板子是zynq7030+AD9363,众筹的板子会在众筹结束后打版。

2、网上那个无线传输视频是用OFDM实现的吗?是PL端实现的还是PS端实现的?

答:是用的OFDM实现的。通过PL端实现,纯逻辑基带,请注意:视频演示是我们在行业领域做得一套通信系统,售价昂贵,不是开放那一套系统的源码,此次课程众筹讲述该类通信系统的核心算法和技术。

3、正点原子的开发板可以兼容吗?

答:开发板相应课程使用ZYNQ器件实现,纯逻辑模块可以在任何FPGA中进行验证,正点原子核心芯片如果使用的是ZYNQ系列则还可以验证PL和PS互联部分,正点原子无法由于不带射频部分,因此射频部分无法验证。(其他黑金等亦类似)

4、我自己有一块xilinx的基础板可以代替使用吗?

答:请确认使用的XILINX的哪个型号的FPGA,纯逻辑部分任何芯片都可以验证,射频部分由于不带射频模块无法验证,和ARM交互部分需要ZYNQ系列才可以验证。

5、OFDM的收发功能在整个工程中是开放的么?培训内容中有没?

答:无线通信主要用于专网和公网基站等,基于OFDM技术的宽带传输和视频编解码配套,适用于无人机图传和影视拍摄;视频演示是我们做的一套系统演示;视频教程主要以我们开发的无线通信系统为主线,串讲无线通信的核心模块,并提供相应模块的算法模型和代码;不是提供一套现成的量产的通信源码,7030的资源没法放下我们演示的整套算法。

6、我想问一下,买一个板子,然后自己配一个rtl sdr,能玩起来不?

答:ADI官方的射频demo板子要3000多,可以做前期验证,此次众筹的板子,我们会提供AD配置寄存器的相关代码及工具。

7、源码是什么形式的?

答:源码是veriog和matlab。

8、无线通信部分有没有解调部分?要不整个系统搭不起来

答:此次众筹课程,主讲发送编码流程,和解码部分定点技巧。不包含接收部分所有源码,之所以会有收发套餐,是有利于读者方便自己产品的原型验证。

9、7030放不下,是哪个那么占资源?

答:不能具体说道哪个模块占资源,是整个系统结构较复杂,组合在一起就导致系统资源较大。

10、1个板子可以玩吗?跟2个板子有什么区别?

答:可以的。课程的所有课程都是可以在一块板子上实现的,视频中的Demo是我们自己做的一整套算法(pin to pin同规模的ZYNQ7035实现),所以课程并没有包含整套图传的源码,而是针对其中的关键模块和核心技术做讲解。之所以会有两块板子的套餐,是考虑到通常的无线通信会有一发一收,为方便客户进行原型验证,因此推出2块板卡的套餐,价格也会更便宜。

11、我想问一下Linux和U-Boot那里讲到什么程度,能深入到板级移植么,就是能讲到将Xilinx官方提供的最新的BSP移植到自己设计的Zynq板子上么?

答:我们会移植在配套的开发版,并在上面跑通1000兆以太网,这个移植有很多细节。这类问题整个软硬件涉及的内容比较广,会在各个模块讲解的时候讲解对系统移植需要注意的问题

12、无线模块,可以实现全双工吗 ?

答:具体要看用户的算法和AD936x的配置了, TDD模式为半双工,用户可以自己做成FDD全双工,我们也侧重讲解FDD的配置。

13、众筹页面上的演示视频,课程上会穿插这个无线图传的实例吗?

答:这个视频是我们做的图传系统,安排的课程就是按照图传的关键技术也就是无线基带的处理流程来讲,从项目立项,芯片选型到算法及量产。

14、这个课程适合用fpga做dds和锁相环的人员听吗?

答:PLL锁相环可以直接调用源语或者IP CORE。DDS网上应该有很多列子,稍微看一下,熟悉下语法就可以了。

15、会讲Matlab和HDL语言的组合仿真吗?

答:会有Matlab和moldesim相互验证仿真,matlab是原型用于验证算法原型,fpga是具体实现

16、这开发板可以用于开发视频或图像处理吗?

答:课程主要讲解FPGA及无线通信的一些技巧,如果仅仅用于验证图像处理的算法,FPGA核心资源是够用的,但是视频处理的接口我们没留(如:HDMI),视频接口需要在自己加接口板,开发板没有提供视频接口。

17、原题图会提供吗?是什么格式的?

答、PDF。

18、我想问下视频中的编码板,和解码板有包含在内吗?

答:我们板子是分核心版和底板。两套板子的套餐就是方便用于验证的自己的程序,一发一收,编码和解码,但板子是一样的。有个细节请注意:我们演示的是我们开发的那一套专业市场算法,我们整套算法是不开源源码的,我们开源的是我们模块的代码和开发无线通信的一些处理技巧和核心思想。

19、算法用hls 开发的吗?

答:HLS其实目前在实际工程中用的公司很少,大部分还是用HDL去实现的,我们整套基带算法都用的是纯逻辑实现。

20、你们用的是verilog吗?不是vhdl吧?

答:是的,用的verilog。我们的仿真模型用的是matlab

21、每一个内容都会有配套视频课程是嘛?

答:是的,还有工程,matlab(涉及到算法的),verilog和 定点。

22、请问不可综合的verilog语句是不是不能烧写到FPGA中只能仿真?

答:不可综合的意思就是不能在FPGA中布线布局,所以不能烧录在FPGA仿真,只能用仿真工具仿真波形。

23、有开发环境的 虚拟机 提供嘛?开发环境 和 工具 软件 都有嘛?

答:课程里面会有搭建过程,安装系统,xilinx的linux操作,Xilinx的软件直接可以在官方下载就好。

24、系统硬件是四天线,是指双收双发支持2*2mimo吗

答:AD9363是双发双收的收发器,硬件支持2×2 MIMO。

25、课程中提到了turbo,ldpc,这些编译码也会在实战中吗?

答:会重点讲解LDPC编码,并提供可供工程应用的源码。除此之外会提供的有整个基带编码的Verilog源码,出调制信号。并重点讲解关键的几个内容模块:FFT,交织,组帧,LDPC等,并详细讲述matlab和Verilog数据比对技巧。解码会详细讲解:量化方法、数学运算化简方式,同步中的滑动累加实现技巧等。

26、众筹买的板子是否提供接收机的加载文件?

答:众筹版本不提供视频演示的基带文件(演示的7035pin to pin封装的图传,这套系统我们有在专业市场出售),但是,我们会提供验证教程中的各模块的源文件和源码。

27、提供整套的源文件吗?

答:(前面已回答该问题)

28、整套课程提供哪些东西?

答:提供的内容:编码部分verilog hdl源码,含LDPC等,文档,matlab,配套核心部分源码讲解(按照众筹的目录)。提供两块板子的初衷:方便学习者进行自己算法原型的验证(不打算卖很多开发板,主打课程,PCB价格已经很低,不到一块zedboard价格)。

29、学图像处理好还是学无线通信好?

答:经验分两种:技术经验和行业经验。

图像和无线通信是两个方向,积累的是行业经验,行业经验不仅仅和FPGA本身相关,FPGA本身只是一个工具。两个行业都挺好,但任何一个行业都有人飞黄腾达,也有人一败涂地。

针对FPGA技术本身,本课程是非常合适学习的,因为我们从课程规划和技术层面的讲解都是从项目角度出发,并站在了一定的高度。

图像和无线通信能走到的高度,最终比的是数学理论和数学应用。但其实大部分工程师的努力程度和经验积累还不足以达到和同行拼数学理论和数学应用。

30、AD9361可以进行回环测试吗?

答:我们的发射测试用的AD9361 BIST模式,整个链路我们在屏蔽房中通过在中间增加衰减器测试灵敏度,用频谱仪和网络分析去测试射频链路质量,回环测试我们没用过,不过我们跟供应商有确认,是可以进行回环测试。

---------------------------------------------------------------------------------------

众筹配套免费直播邀您观看

【5G关键技术】FPGA无线通信开发第1期:FPGA无线通信开发—开篇

直播链接:https://t.elecfans.com/live/839.html

【5G关键技术】FPGA无线通信开发第2期:项目立项

直播链接:https://t.elecfans.com/live/840.html

【5G关键技术】FPGA无线通信开发第3期:Verilog——最“硬”的语言

直播链接:https://t.elecfans.com/live/841.html

【5G关键技术】对话FPGA原厂—既聊技术,也谈市场

一个从业十几年的FPGA工程师看完目录告诉你,垃圾~

hamugeduo:除了点评一句垃圾,还会说别的吗?觉得不好,就说哪不好?把道理摆明白,从业十几年也没见素质!(2019-06-22)

okiohj:有这么大成就后站出来传授知识本身就是值得人尊敬的!赞(2019-05-22)

我手头有Adam Pluto 能兼容不?

lzr858585:adam pluto应该不兼容哦~开发板相应课程使用ZYNQ器件实现,纯逻辑模块可以在任何FPGA中进行验证,正点原子核心芯片如果使用的是ZYNQ系列则还可以验证PL和PS互联部分,正点原子无法由于不带射频部分,因此射频部分无法验证。(2019-06-06)

这个是交智商税的吗?

hamugeduo:是啊,哪里都有收智商税的。既然觉得教程简单,那就分们别类的说一说简单在哪里。把道理摆摆清楚!(2019-06-22)

zzzwp1111:我也觉得,哈哈哈,忽悠,基础和进阶教程,,,我只想说,呵呵(2019-05-08)

我是硬件工程师和linux驱动工程师,想学FPGA,请问:1.零基础不懂Verilog(C语言基础)可不可以学?,2.有没有线下培训的方式,然后我们公司出钱,如果有,是什么流程?

myj1989221:你咋会这么多?(2019-04-29)